# UNIVERSIDAD AUTÓNOMA DEL ESTADO DE HIDALGO

INSTITUTO DE CIENCIAS BÁSICAS E INGENIERÍA

ING. EN ELECTRÓNICA Y TELECOMUNICACIONES

SISTEMA CALIFICADOR DE EXÁMENES

## **MONOGRAFÍA**

QUE PARA OBTENER EL TÍTULO DE INGENIERO EN ELECTRÓNICA Y TELECOMUNICACIONES

PRESENTA: RUBÉN ESCORCIA RÍOS

ASESOR: M. EN C. ELÍAS VARELA PAZ

PACHUCA DE SOTO, HGO. DICIEMBRE DE 2008.

Agradecimientos.

A mis padres por su apoyo incansable, por el cariño y la paciencia que me han impulsado a cumplir con una meta más.

Al M. en C. Elías Varela Paz por el gran apoyo y tiempo dedicado para concluir este trabajo.

#### Resumen

Este proyecto consiste en el diseño y construcción de un sistema computarizado de calificación de exámenes, elaborados en formatos comunes y corrientes, contestados por los alumnos mediante marcas en recuadros hechas a lápiz.

Con este trabajo se pretende ofrecer un método para aligerar el trabajo que representa la generación, calificación e impresión de exámenes; mediante la automatización computacional. Sus principales características residen en el ámbito económico, independencia tecnológica y simplicidad, esto debido a que está pensado para ser integrado, utilizando en una primera fase elementos puramente electrónicos, en lo que será la etapa de creación de hardware y posteriormente, en una segunda y tercer fase de este trabajo (etapa de software), usando un microcontrolador PIC o cualquier computadora personal, incluso de muy baja capacidad (como las PC Intel 8088), dando de esta forma un carácter de aprovechamiento de equipo en apoyo a las economías tercermundistas como la de nuestro país. Las hojas empleadas para introducir las respuestas se basan en la tecnología de lector óptico (Tipo CENEVAL), pero con la particularidad de que se emplean hojas comunes con un formato de fácil acceso y diseño.

Además, se ha intentado establecer una estructura abierta en el sentido de que el programa tenga posibilidades de evolucionar tanto en sus bancos de datos como en su estructura, para lo cual se entregarían al adquiriente del equipo, no solamente los programas ejecutables y toda la información necesaria para su construcción, sino también el programa fuente.

Este proyecto tiene una alta complejidad y por lo tanto se ha seccionado en tres trabajos de tesis: Uno para resolver la parte electrónica y de ensamblaje mecánico, otra para la parte de interfaz de usuario y finalmente, una para el sistema de solución, registro e información oficial de los resultados de examen para cada alumno.

En la sección referida de interfaz de usuario, se pretende ofrecer un servicio amigable para que el profesor sea capaz de introducir sus reactivos de examen en forma ágil y cómoda, aun sin tener conocimientos de programación; además, será posible escoger aleatoriamente los reactivos de su banco de reactivos (problemario) para configurar los exámenes personalizados para ser aplicados a su grupo de alumnos. Como se ve, estos y otros detalles de la interfaz parecen sencillos pero resultan sumamente complejos y se requiere de por lo menos otro pasante para ello.

De igual manera podríamos decir de las otras capas del trabajo de programación, que debe participar un buen número de especialidades para dar respuesta a la solución de los diferentes reactivos que contendrán temas de física, matemáticas, electrónica, o cualquier materia que se desee. Pero la parte mas ingeniosa podría ser la capacidad que deberá tener este sistema para permitir al usuario, la incorporación de fórmulas de solución dentro de su acervo matemático para atender a alguna nueva disciplina.

### **ÍNDICE GENERAL**

| CAPÍTULO I. INTRODUCCIÓN                                |    |

|---------------------------------------------------------|----|

| 1.1 Descripción general.                                | 7  |

| 1.2 Objetivos.                                          | 9  |

| 1.3 Justificación.                                      | 9  |

| 1.4 Alcance del trabajo.                                | 12 |

| 1.5 Hipótesis.                                          | 12 |

| 1.31 lipotesis.                                         | 12 |

| CAPÍTULO II. MARCO TEÓRICO                              |    |

| 2.1 El fototransistor.                                  | 14 |

| 2.1.1 El fototransistor PT331.                          | 15 |

| 2.2 El multiplexor.                                     | 18 |

| 2.2.1 Multiplexor/Demultiplexor con 16 canales análogos |    |

| HEF4067BP.                                              | 19 |

| 2.3 Microcontroladores.                                 | 22 |

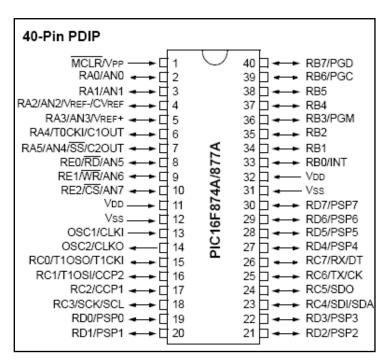

| 2.3.1 Microcontrolador PIC 16F877A                      | 24 |

| 2.3.1.1 Diagrama a bloques del PIC 16F877A              | 26 |

| 2.3.1.2 Descripción de la CPU.                          | 27 |

| 2.3.1.3 Registro de la CPU.                             | 27 |

| 2.3.1.4 Organización de la memoria del PIC.             | 29 |

| 2.3.1.5 Memoria de datos.                               | 29 |

| 2.3.1.6 Bancos de memoria.                              | 29 |

| 2.3.1.7 Archivos de registro.                           | 30 |

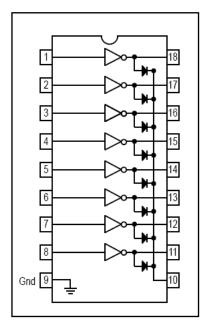

| 2.4 Arreglo Darlington de transistores.                 | 32 |

| 2.4.1 Arreglo Darlington de transistores ULN2803A.      | 33 |

| 2.5 Motores a pasos.                                    | 35 |

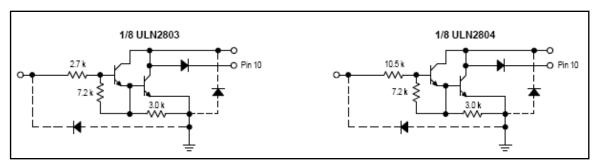

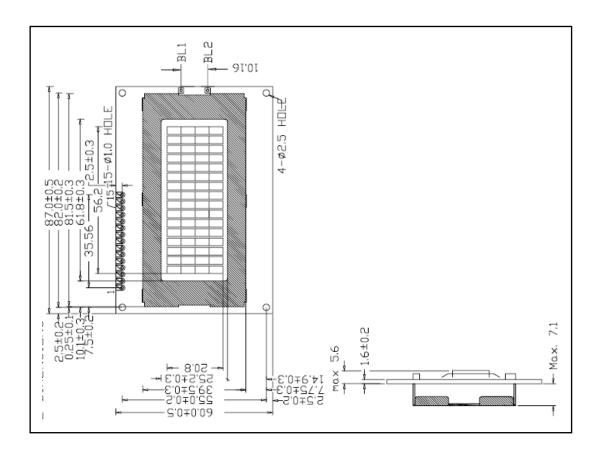

| 2.6 Pantalla LCD.                                       | 36 |

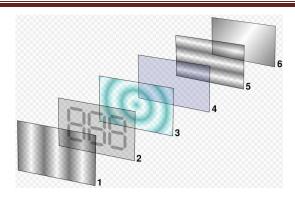

| 2.6.1 Pantalla LCD LM4433.                              | 37 |

| CAPÍTULO III PROBLEMÁTICA.                                     |    |

|----------------------------------------------------------------|----|

| 3.1 Descripción del problema.                                  | 38 |

| CAPÍTULO IV ESTADO DEL ARTE.                                   |    |

|                                                                | 40 |

| 4.1 Sistemas de lectura óptica para exámenes en papel impreso. | 43 |

| CAPÍTULO V SOLUCIÓN PROPUESTA.                                 |    |

| 5.1 Identificación de necesidades y características.           | 47 |

| 5.2 Diseño del sistema óptico.                                 | 50 |

| 5.3 Movilidad del lector.                                      | 52 |

| 5.4 Iluminación.                                               | 53 |

| 5.5 Multiplexión.                                              | 53 |

| 5.6 Diseño de la hoja de respuestas.                           | 55 |

| 5.7 Teclado.                                                   | 56 |

| 5.8 Pantalla LCD.                                              | 56 |

| 5.9 Diseño de la etapa de control.                             | 59 |

| 5.10 Diseño del programa de adquisición.                       | 60 |

|                                                                |    |

| CONCLUSIONES                                                   | 63 |

| BIBLIOGRAFÍA                                                   | 64 |

| ANEXOS                                                         | 65 |

|            | Índice de figuras.                                         |    |

|------------|------------------------------------------------------------|----|

| 2 Marco te | eórico.                                                    |    |

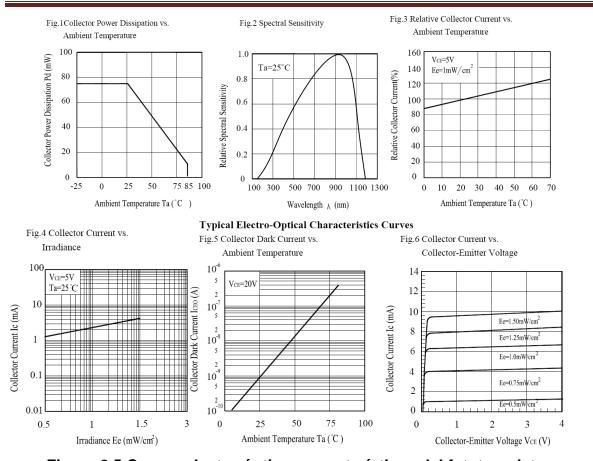

| 2.1        | Fototransistor.                                            | 14 |

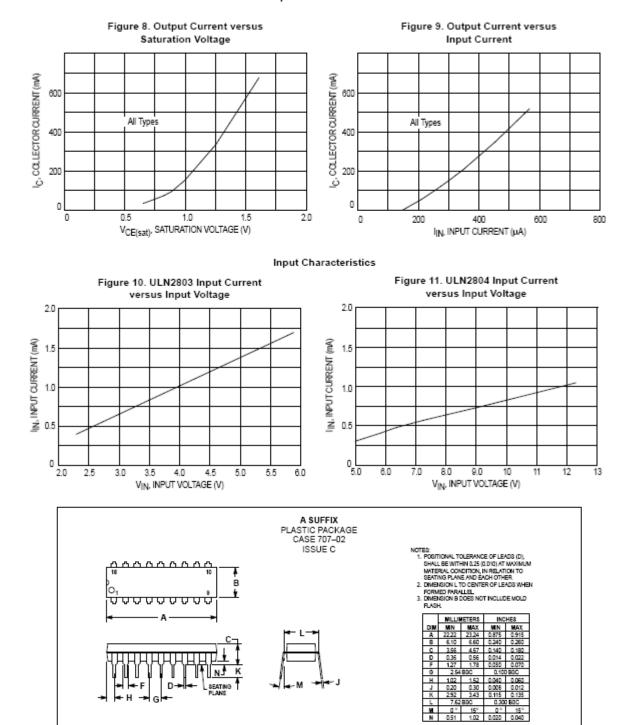

| 2.2        | Características radiantes y eléctricas del fototransistor. | 15 |

| 2.3        | Dimensiones del fototransistor.                            | 16 |

| 2.4        | Características electro-ópticas.                           | 17 |

| 2.5        | Curvas electro-ópticas características del fototransistor. | 18 |

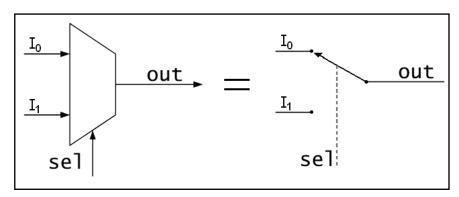

| 2.6        | Multiplexor.                                               | 19 |

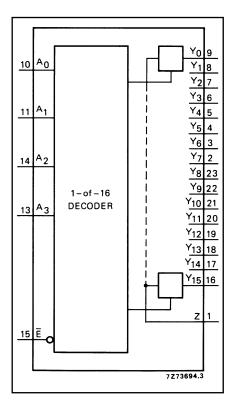

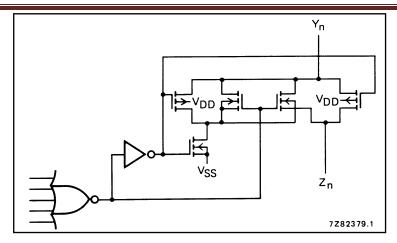

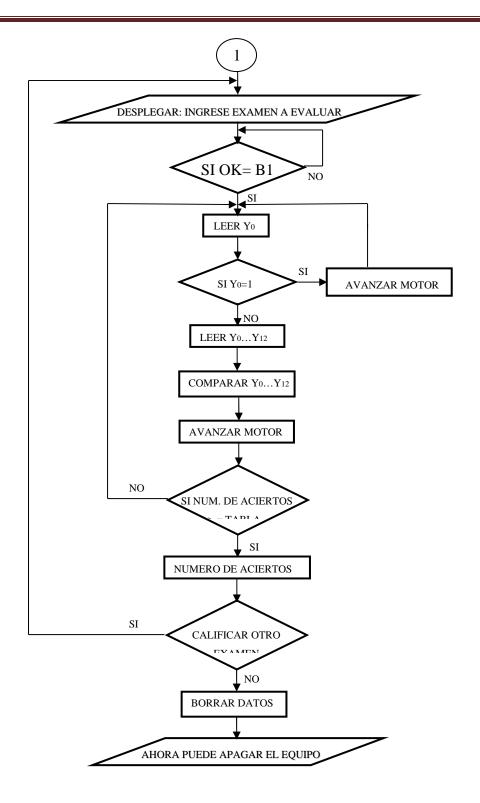

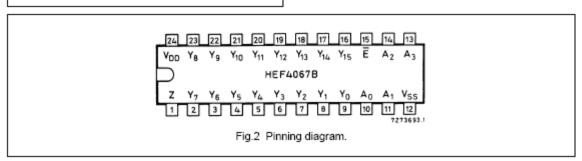

| 2.7        | Diagrama funcional del HEF4067B.                           | 20 |

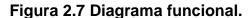

| 2.8        | Diagrama de pines del HEF4067 B.                           | 20 |

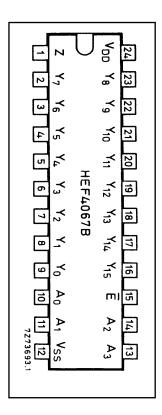

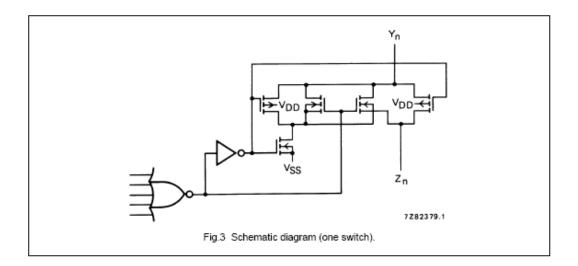

| 2.9        | Diagrama esquemático de cada uno de los switches.          | 21 |

| 2.10       | Tabla de verdad del HEF4067B.                              | 21 |

| 2.11       | Diagrama interno.                                          | 22 |

| 2.12       | Microcontrolador PIC.                                      | 23 |

| 2.13       | Diagrama de pines PIC16F877A.                              | 25 |

| 2.14       | Diagrama a bloques PIC16F877A.                             | 26 |

| 2.15       | Registro Status.                                           | 27 |

| 2.16       | Tabla de instrucciones del PIC16F877A.                     | 28 |

| 2.17       | Bancos de memoria.                                         | 30 |

| 2.18       | Mapa de archivo de registros.                              | 31 |

Amplificador Darlington básico.

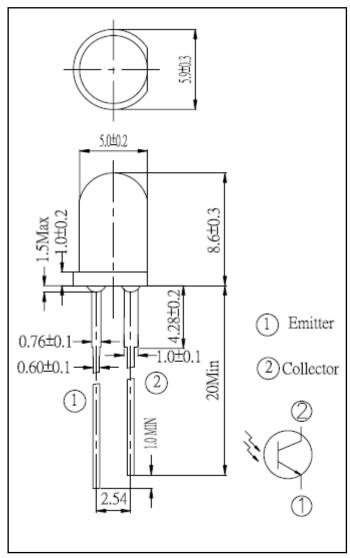

Características del ULN2803.

Dimensiones y encapsulado.

Diagrama esquemático.

Dimensiones del display.

Descripción de la interfaz.

Esquema de conexiones del display.

Motores a pasos.

Pantalla LCD.

Diagrama de conexiones Driver ULN2803.

2.19

2.20

2.21

2.22

2.23

2.24

2.25

2.26

2.27

2.28

32

33

34

34

35

36

37

37

38

38

| 3 Problemática.                                     |    |

|-----------------------------------------------------|----|

| 3.1 Diagrama a bloques del sistema.                 | 41 |

| 4 Estado del arte.                                  |    |

| 4.1 Ilustración de los formatos de hoja especiales. | 43 |

| 4.2 Sistemas comerciales                            | 44 |

| 4.3 Ilustración.                                    | 45 |

| 4.4 Otros ejemplos.                                 | 45 |

| 4.5 Tecnología ICR, OCR Y OMR.                      | 46 |

| 5 Solución propuesta.                               |    |

| 5.1 Funcionamiento del sistema óptico pretendido.   | 49 |

| 5.2 Modelo propuesto.                               | 50 |

| 5.3 Sistema óptico.                                 | 51 |

| 5.4 Posición de los sensores ópticos.               | 51 |

| 5.5 Diagrama esquemático del ULN2803A.              | 52 |

| 5.6 Tabla de verdad del HEF4067BP.                  | 54 |

| 5.7 Diagrama funcional.                             | 55 |

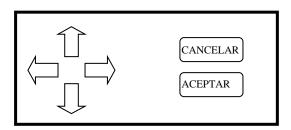

| 5.8 Teclado.                                        | 56 |

| 5.9 Pantalla LCD.                                   | 57 |

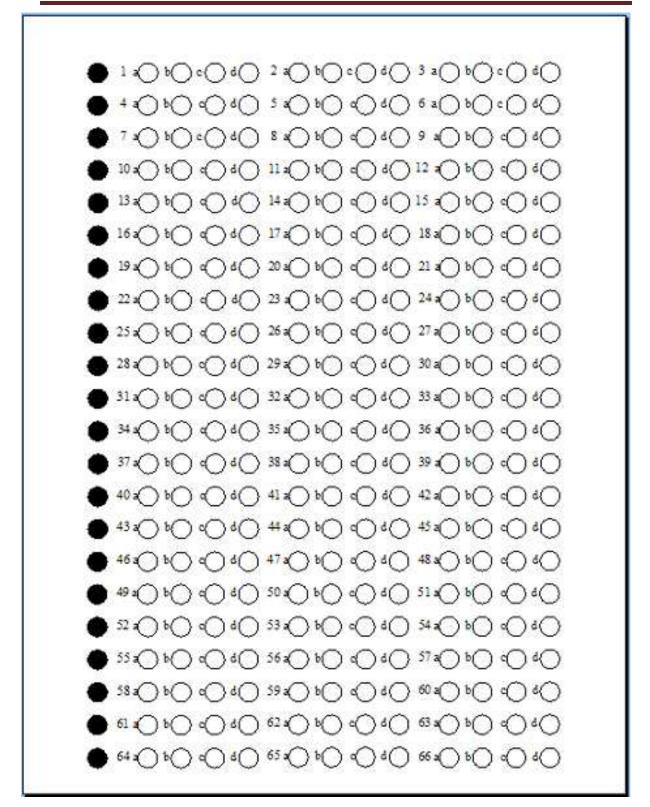

| 5.10 Formato de la hoja de respuestas.              | 58 |

| 5.11 PIC16F877A                                     | 59 |

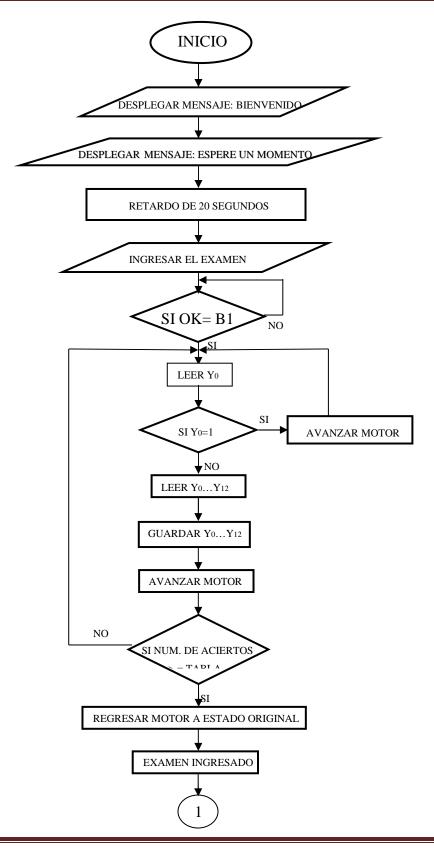

| 5 12 Diagrama de fluio                              | 61 |

### CAPÍTULO I. INTRODUCCIÓN.

#### 1.1 DESCRIPCIÓN GENERAL

La propuesta de este trabajo es un sistema que permite a los docentes aplicar los exámenes mediante una hoja descriptiva de los detalles de las preguntas, ya sean de opción múltiple, problemas o mixto. Pero el alumno responderá en una hoja de respuestas preestablecida, obscureciendo mediante lápiz los espacios que estén de acuerdo a sus respuestas.

Estas hojas de datos o formato de hoja de respuestas serán colocadas en un artefacto lector óptico, en primer lugar la hoja con las respuestas correctas o clave del docente, el sistema leerá estas respuestas que reconocerá como validas y guardara en la memoria del sistema, posterior a esto, se solicitará el ingreso de la hoja de respuestas a evaluar y el sistema óptico leerá los datos obtenidos de igual manera, una vez leídos estos datos serán traducidos a respuestas que, después de ser comparadas con la base de datos correctos del sistema que ingresamos en primer lugar, se calculará la calificación y se le presentará al usuario para mostrarle la puntuación que el alumno merece, resultado que desde ese momento aparecerá en forma inamovible.

El sistema impactará no sólo en la rapidez y eficiencia de la calificación en sí misma, sino en la implantación de una base de datos creciente que apoyará al maestro en su labor docente y académica. Esto es debido a que el sistema contendrá un módulo de algoritmos de cálculo que permitirá actualizar la base de datos. Este diseño pretende ser de tal forma que al catedrático le sea posible, introducir nuevos reactivos, sean de opción múltiple o problemas de cálculo, además de modificar los valores que se dan como datos en los problemas. Además, todos los reactivos estarían disponibles para ulteriores exámenes, de entre los cuales se presentará al maestro una muestra aleatoria para conformar su examen, de tal manera que cada examen resulte diferente pero con el mismo nivel de dificultad. Adicionalmente en hipótesis, este sistema permitiría incorporar

elementos que le darían aún mayor brillo, como por ejemplo, la facilidad de utilizar los mismos problemas para los alumnos de un mismo grupo pero con la libertad de cambiar los datos que se dan en el enunciado. Todo esto mediante la flexibilidad otorgada al sistema por un bien estructurado y amigable programa de computadora (interfaz hombre-máquina).

Desde luego, el sistema planteado hasta aquí resulta muy complicado para circunscribirlo en un solo trabajo de tesis, así que de acuerdo a lo planteado por el asesor de este trabajo, se ha decidido resolverlo mediante por lo menos dos participaciones: un trabajo de la parte electrónica o de bajo nivel que es la que se esta presentando y otro trabajo del área de sistemas computacionales a nivel de software.

En forma resumida, las prestaciones principales que este sistema ofrecerá al usuario son:

- -Diseño de exámenes con alternativas de opción múltiple y planteamiento de problemas. Esto mediante la selección aleatoria de reactivos existentes en una base de datos (problemario)

- -Permitirá el crecimiento de la base de datos conforme los maestros vayan introduciendo nuevos reactivos.

- -Ofrecerá la libertad de que el maestro escoja solamente resultados terminales y/o resultados parciales equivalente a lo que se conoce en el medio estudiantil como calificar procedimiento.

- -Presentación de resultados e historial de calificaciones del periodo hasta el momento.

#### 1.2 OBJETIVOS

Como objetivo general y de mayor importancia del trabajo es el de crear y ofrecer a la comunidad un sistema autónomo que permita el diseño, generación y aplicación de exámenes, basado en recursos muy económicos para que resulte lo más accesible posible, con el afán de disminuir la ardua labor docente que representa el calificar exámenes, todo esto mediante un sistema económico, que apoye a las débiles economías de países como el nuestro.

#### Otros objetivos serían:

- -Brindar al profesor una ayuda eficiente y atractiva para el diseño, generación, aplicación y evaluación de exámenes.

- -Reducir tiempos y esfuerzos en la calificación de exámenes, los cuales pueden ser utilizados en la preparación de clases.

- Evitar vicios en la aplicación de exámenes, por parte de los profesores y de los alumnos.

- Lograr uniformidad en los temas estudiados y evaluados en cada materia, apegándose a la programación curricular.

- Permitir exámenes departamentales que coadyuven a la eficiencia y seguimiento de avances programáticos.

### 1.3 JUSTIFICACIÓN

La labor docente representa una constante, rutinaria y paciente actividad sobre los alumnos, de parte de los profesores, empeñada en formar a estos de manera integral y eficiente, cuyo impacto se puede dilucidar mediante las evaluaciones periódicas que el maestro y los reglamentos señalen. Esta parte de la labor del maestro arrojará un diagnóstico tan fiel en la medida que las evaluaciones se

hagan con mayor frecuencia, de aquí el concepto de "evaluación continua" que algunas corrientes del pensamiento didáctico defienden tanto.

Para todos es conocido que la labor más pesada de los docentes por el momento, es el proceso de calificación de exámenes, especialmente en los países como el nuestro, en el cual no se encuentra automatizado este proceso y debe de llevarse a cabo una exhaustiva revisión de todos y cada uno de los reactivos que conforman el examen, de un total de alumnos que a veces sobrepasa la media centena.

Además, para lograr una evaluación integral, basada en un criterio justo, muchos maestros deben analizar no solamente el resultado arrojado por el procedimiento de cálculo que cada alumno determine y que suele ser diferente, sino también las decisiones que se tomaron durante tal procedimiento y los resultados intermedios que frecuentemente son minúsculos pero provocan, al final, un resultado muy distinto al correcto.

Ante un compromiso entre la necesidad de una evaluación continua, que permita mantener al maestro informado de los avances que el alumnado va logrando y la realidad de respuesta limitada de parte del maestro para esta labor, el sentido común arroja la concluyente opción de asumir un término medio de equilibrio, en que existe una mediana frecuencia de evaluación y una carga de trabajo por parte del maestro que no deja de ser agotadora.

La tarea abrumadora que se presenta al maestro con el proceso de evaluación da como resultado que él opte por dos posiciones:

- a)Respetar las disposiciones establecidas y entregarse a esa agotadora tarea aún a expensas de su tiempo libre y el deterioro de la tranquilidad de su vida tanto social, personal como familiar.

- b)Incumplir las disposiciones reglamentarias llevando a cabo una actividad de evaluación incompleta centrada en la apariencia por entrega de resultados en tiempo y forma, aunque seguramente injusta.

Estos argumentos orillan a desear un método que permita al maestro generar, calificar e imprimir sus exámenes de manera ágil y eficiente para dedicar su tiempo a las labores que le reclaman con mayor importancia: preparar e impartir sus clases.

En este trabajo se presenta una solución económica, sencilla, pero eficaz que responde a la mayoría de los casos de examen existentes en cualquier nivel de estudios: La automatización del proceso de calificación de exámenes mediante lectores ópticos.

Por otro lado, la exigencia de construir un sistema económico, que puedan utilizar las comunidades más marginadas de nuestro territorio nacional, nos obliga a excluir herramientas tan modernas como Internet. Esto porque, si bien es cierto que esta red ofrece una multitud de posibilidades y llega a una enorme cantidad de individuos en el mundo, también es cierto que el acceso a ella por todas las escuelas públicas es, hoy por hoy, un sueño; especialmente en las regiones rurales y semi-urbanas del tercer mundo. Aunado a esto, podemos extender la aplicación de este argumento hacia las escuelas particulares que juegan un papel importante en la solución de la educación en México.

Así que, parece ser una opción más realista el basarse en equipos de fácil consecución como equipos de escaneo anticuadas que se encuentran arrumbadas en calidad de desecho. Con esto también estaríamos siendo congruentes con la realidad económica que también presenta nuestro país.

El alumno realizará sus cálculos en hojas aparte, de la manera tradicional, y cuando obtenga el resultado lo plasmará en la hoja de respuestas. Las hojas de respuesta serán de un formato sencillo y pueden ser de papel común, estos formatos se podrán obtener a través de un modelo establecido y se podrán reproducir libremente de acuerdo a las necesidades de la institución educativa que utilice es sistema o del mismo docente, este formato deberá ser llenado a lápiz por el alumno, en los espacios dispuestos para ello.

#### 1.4 ALCANCE DEL TRABAJO

Aunque las características de este proyecto tienen limitaciones de tipo económico, sus alcances son suficientemente amplios como para competir funcionalmente con otros de su tipo, es decir, será capaz de calificar exámenes con opciones a escoger por el maestro, esto lo realizará de forma rápida y el maestro obtendrá instantáneamente la calificación de cada examen en una pantalla del tipo LCD y así acelerará el proceso de evaluación del alumno.

Como los demás proyectos de su tipo (a saber), el proyecto adolece de ciertas limitaciones propias de un sistema con escasa inteligencia para poder responder a funciones complejas, como la calificación de exámenes en donde predominan funciones de reconocimiento de imágenes o formas, como es el caso de identificación de fórmulas aritméticas.

Por otro lado, a diferencia de los demás, la estructura que se le pretende dar, permitirá abordar la evaluación del procedimiento dentro de la solución de problemas típicos de materias como Física, Matemáticas o Ingeniería. En otras palabras, el docente determinara si calificará procedimiento o solo tomará en cuenta el resultado final de cada problema y esto lo establecerá entre las opciones del examen diseñado.

### 1.5 HIPÓTESIS

El acceso de los maestros a este sistema, permitirá una evaluación continua de los alumnos, esto quiere decir que en la dinámica del curso se implementará n exámenes semanales o con la frecuencia que el docente lo requiera y así lograr una evaluación más eficaz.

Tomando en cuenta la flexibilidad y economía del sistema, será posible que cada plantel educativo cuente con los sistemas necesarios de acuerdo a su plantilla académica y población estudiantil para facilitar y acelerar la evaluación continua ya mencionada.

En hipótesis, también está la posibilidad de que en una segunda parte de esta tesis, sea posible la conectividad con la PC y de esta forma sea posible la creación de bases de datos que permitan al catedrático introducir nuevos reactivos, sean de opción múltiple o problemas de cálculo, además de modificar los valores que se dan como datos en los problemas, todos estos reactivos estarían disponibles para ulteriores exámenes, de entre los cuales se presentará al maestro una muestra aleatoria para conformar su examen, de tal manera que cada examen resulte diferente pero con el mismo nivel de dificultad.

En este sentido, hay que aclarar que la elaboración de todas las funciones antes mencionadas reclama un trabajo de programación de buen nivel y se espera contar en un futuro inmediato con la colaboración de un tesista dedicado a esta tarea.

### CAPÍTULO II. MARCO TEÓRICO.

#### 2.1 EL FOTOTRANSISTOR

Se llama fototransistor a un transistor sensible a la luz, normalmente a los infrarrojos. La luz incide sobre la región de base, generando portadores en ella. Esta carga de base lleva el transistor al estado de conducción. El fototransistor es más sensible que el fotodiodo por el efecto de ganancia propio del transistor.

En el mercado se encuentran fototransistores tanto con conexión de base como sin ella y tanto en cápsulas plásticas como metálicas provistas de una lente (Fig. 2.1).

Se han utilizado en lectores de cinta y tarjetas perforadas, lápices ópticos, etc. Para comunicaciones con fibra óptica se prefiere usar detectores con fotodiodos pi-n. También se pueden utilizar en la detección de objetos cercanos cuando forman parte de un sensor de proximidad.

Se utilizan ampliamente encapsulados conjuntamente con un LED, formando interruptores ópticos (*opto-switch*), que detectan la interrupción del haz de luz por un objeto. Existen en dos versiones: de transmisión y de reflexión.

Figura 2.1 Fototransistor.

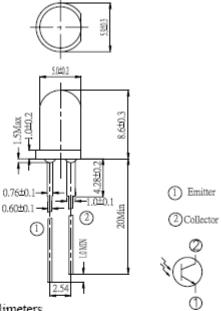

#### 2.1.1 Fototransistor PT331

Con características estables. Su encapsulado es de plástico. Se aplica principalmente en: sistemas de control automático, control remoto, alarmas, fotodetectores, detectores de humo, usos industriales, entre otros.

Las características principales de este dispositivo se muestran en las siguientes tablas y figuras.

#### Máximos rangos absolutos:

Voltaje de sostenimiento de colector a emisor 30 V

Voltaje de ruptura colector emisor 5 V

Corriente de colector 25 mA

Rango de temperatura de operación -40°C~85°C

Rango de temperatura de almacenamiento -40°C~85°C

Temperatura de soldeo 260°C

Humedad relativa a 85°C 85%

Potencia de disipación a (o abajo) de 25°C 100mW

| Parámetro                                           | Símbolo      | Mín. | Tip | Máx | Unidad | Condiciones                 |

|-----------------------------------------------------|--------------|------|-----|-----|--------|-----------------------------|

| Voltaje de<br>sostenimiento de<br>colector a emisor | VCE<br>(SUS) |      | 1.3 | 1.7 | V      | IC = 100 μA<br>H = 0        |

| Voltaje de ruptura<br>de emisor a<br>colector       | BVECO        |      |     | 10  | μА     | IC = 100 μA<br>H = 0        |

| Voltaje de<br>saturación de<br>colector a emisor    | VCE<br>(SAT) | 6    | 10  |     | mW     | IC = 0.5 mA<br>H = 20 mW/cm |

| Corriente en la<br>obscuridad                       | ID           |      | 940 |     | nm     | VCE= 15 V<br>H = 0          |

| Corriente del foto,<br>fuente de tungsteno          | IL           | 1.0  | 20  |     | mA     | VCE= 5 V<br>H = 20 mW/cm    |

| Tiempo de<br>elevación                              | TR           |      | 5   |     | μS     | VCC = 30 V<br>IL = 800 μA   |

| Tiempo de caída                                     | TF           |      | 5   |     | μS     | RL = 1 KOHM                 |

Figura 2.2 Características radiantes y eléctricas del fototransistor.

- 1. Todas las dimensiones son en milímetros

- 2. El rango de tolerancia en las dimensiones es de  $\pm 0.25$ mm

Figura 2.3 Dimensiones del fototransistor.

## Absolute Maximum Ratings (Ta=25°C)

| <b>Parameter</b>                                          | Symbol           | Rating      | Units                  |

|-----------------------------------------------------------|------------------|-------------|------------------------|

| Collector-Emitter Voltage                                 | $V_{\text{CEO}}$ | 30          | V                      |

| Emitter-Collector-Voltage                                 | $V_{\text{ECO}}$ | 5           | V                      |

| Collector Current                                         | $I_{C}$          | 20          | mA                     |

| Operating Temperature                                     | Topr             | -25 ~ +85°C | $^{\circ}\mathbb{C}$   |

| Storage Temperature                                       | Tstg             | -40 ~ +85°C | $^{\circ}\!\mathbb{C}$ |

| Lead Soldering Temperature                                | Tsol             | 260         | $^{\circ}\!\mathbb{C}$ |

| Power Dissipation at (or below) 25°C Free Air Temperature | Рс               | 75          | mW                     |

**Notes:** \*1:Soldering time ≤ 5 seconds.

### Electro-Optical Characteristics (Ta=25°C)

| Parameter                                | Symbol                       | Condition                                      | Min. | Typ.     | Max. | Units   |

|------------------------------------------|------------------------------|------------------------------------------------|------|----------|------|---------|

| Collector – Emitter<br>Breakdown Voltage | BV <sub>CEO</sub>            | $I_C=100 \mu A$<br>Ee=0mW/cm <sup>2</sup>      | 30   |          |      | V       |

| Emitter-Collector<br>Breakdown Voltage   | $\mathrm{BV}_{\mathrm{ECO}}$ | $I_E=100 \mu A$<br>$Ee=0mW/cm^2$               | 5    |          |      | V       |

| Collector-Emitter<br>Saturation Voltage  | V <sub>CE)(sat)</sub>        | I <sub>C</sub> =2mA<br>Ee=1mW/cm <sup>2</sup>  |      |          | 0.4  | V       |

| Rise Time                                | t <sub>r</sub>               | V <sub>CE</sub> =5V                            |      | 15       |      |         |

| Fall Time                                | $t_{\mathbf{f}}$             | $I_{C}=mA$ $RL=1000\Omega$                     |      | 15       |      | $\mu$ S |

| Collector Dark Current                   | $I_{CEO}$                    | Ee=0mW/cm <sup>2</sup><br>V <sub>CE</sub> =20V |      |          | 100  | nA      |

| On State Collector Current               | I <sub>C(on)</sub>           | Ee=1mW/cm <sup>2</sup><br>V <sub>CE</sub> =5V  | 0.7  | 2.5      |      | mA      |

| Wavelength of<br>Peak Sensitivity        | λр                           |                                                |      | 940      |      | nm      |

| Rang of Spectral Bandwidth               | λ 0.5                        |                                                |      | 400-1100 |      | nm      |

Figura 2.4 Características electro-ópticas.

Figura 2.5 Curvas electro-ópticas características del fototransistor.

#### 2.2 MULTIPLEXOR

En electrónica digital, un multiplexor, es un circuito usado para el control de un flujo de información que equivale a un conmutador. En su forma más básica se compone de dos entradas de datos (A y B), una salida de datos y una entrada de control (Fig. 2.6). Cuando la entrada de control se pone a 0 lógico, la señal de datos A es conectada a la salida; cuando la entrada de control se pone a 1 lógico, la señal de datos B es la que se conecta a la salida...

El multiplexor es una aplicación particular de los decodificadores, tal que existe una entrada de habilitación por cada puerta AND y al final se hace un OR entre todas las salidas de las puertas AND.

La función de un multiplexor da lugar a diversas aplicaciones:

Selector de entradas.

Serializador: Convierte datos desde el formato paralelo al formato serie.

Transmisión multiplexada: Utilizando las mismas líneas de conexión, se transmiten diferentes datos de distinta procedencia.

Realización de funciones lógicas: Utilizando inversores y conectando a 0 ó 1 las entradas según interese, se consigue diseñar funciones complejas, de un modo más compacto que con las tradicionales puertas lógicas.

Figura 2.6 Multiplexor.

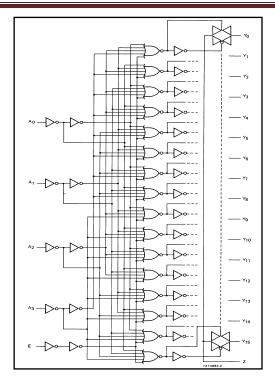

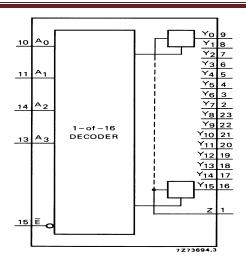

#### 2.2.1 Multiplexor/Demultiplexor con 16 canales análogos HEF4067BP

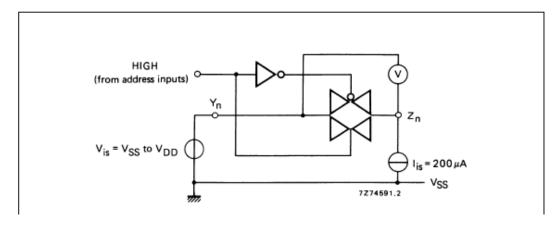

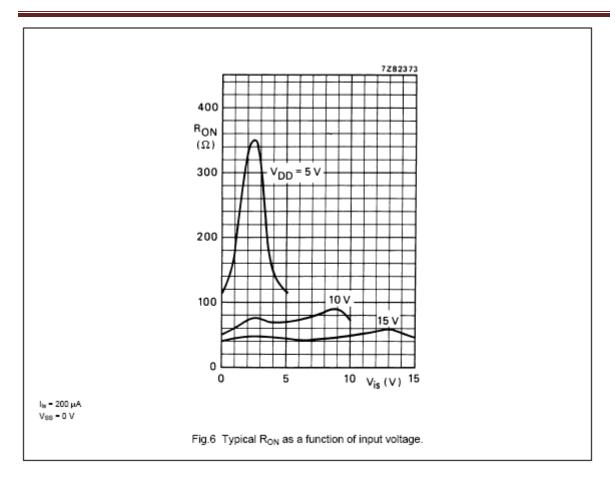

El HEF4067B es un multiplexor/demultiplexor de 16 canales analógicos con cuatro entradas de dirección (A0 a A3), con una entrada (Ē) de habilitación en baja (low), dieciséis entradas/salidas independientes (Y0 a Y15) y una entrada/salida (Z) (Fig.2.7).

El dispositivo contiene dieciséis interruptores analógicos bidireccionales, cada uno conectado a una entrada/salida independiente (Y0 a Y15) y el otro lado conectado al común de entrada/salida (Z).

Cuando Ē está en estado bajo (0 volts) una de las 16 entradas/salidas es seleccionada por A0...A3 (baja impedancia, estado activo). Todas las entradas/salidas no seleccionadas restantes estarán inactivas. Cuando Ē este en

estado alto (5 volts) todas las 16 entradas/salidas estarán inactivas, independientemente de A0...A3, como lo muestra la tabla de verdad de la figura 2.10.

Las entradas/salidas (Y0...Y15 y Z) pueden variar entre VDD como un límite positivo y VSS como limite negativo. La diferencia entre VDD y VSS no debe exceder los 15 volts.

Figura 2.8 Diagrama de pines.

Figura 2.9 Diagrama esquemático de cada uno de los switches.

|   | II                    | NPUTS          |                       |                | CHANNEL             |

|---|-----------------------|----------------|-----------------------|----------------|---------------------|

| Ē | <b>A</b> <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> | ON                  |

| L | L                     | L              | L                     | L              | $Y_0 - Z$           |

| L | L                     | L              | L                     | Н              | $Y_1 - Z$           |

| L | L                     | L              | Н                     | L              | $Y_2 - Z$           |

| L | L                     | L              | Н                     | Н              | Y <sub>3</sub> – Z  |

| L | L                     | Н              | L                     | L              | $Y_4 - Z$           |

| L | L                     | Н              | L                     | Н              | Y <sub>5</sub> – Z  |

| L | L                     | Н              | Н                     | L              | $Y_6 - Z$           |

| L | L                     | Н              | Н                     | Н              | Y <sub>7</sub> – Z  |

| L | Н                     | L              | L                     | L              | Y <sub>8</sub> – Z  |

| L | Н                     | L              | L                     | Н              | Y <sub>9</sub> – Z  |

| L | Н                     | L              | Н                     | L              | $Y_{10} - Z$        |

| L | Н                     | L              | Н                     | Н              | Y <sub>11</sub> – Z |

| L | Н                     | Н              | L                     | L              | Y <sub>12</sub> – Z |

| L | Н                     | Н              | L                     | Н              | Y <sub>13</sub> – Z |

| L | Н                     | Н              | Н                     | L              | Y <sub>14</sub> – Z |

| L | Н                     | Н              | Н                     | Н              | Y <sub>15</sub> – Z |

| Н | Х                     | Х              | Х                     | Χ              | none                |

Nota:

H= High state (mayor voltaje positivo)

L= Low state (menor voltaje positivo)

X= Estado de no importa

Figura 2.10 Tabla de verdad HEF4067BP.

Figura 2.11 Diagrama interno HEF4067BP.

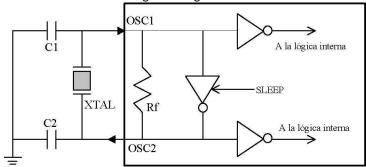

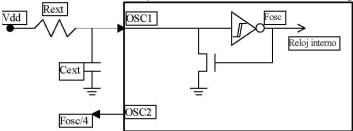

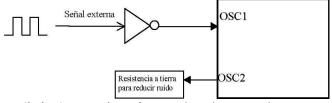

#### 2.3 MICROCONTROLADORES PIC

Los "PIC" son una familia de microcontroladores tipo RISC fabricados por Microchip Technology Inc. y derivados del PIC1650, originalmente desarrollado por la división de microelectrónica de General Instruments.

El nombre actual no es un acrónimo. En realidad, el nombre completo es PICmicro, aunque generalmente se utiliza como Peripheral Interface Controller (Controlador de Interfaz Periférico).

El PIC original se diseñó para ser usado con la nueva UCP de 16 bits CP16000. Siendo en general una buena UCP, esta tenía malas prestaciones de E/S, y el PIC de 8 bits se desarrolló en 1975 para mejorar el rendimiento del sistema quitando peso de E/S a la UCP. El PIC utilizaba microcódigo simple almacenado en ROM

para realizar estas tareas; y aunque el término no se usaba por aquel entonces, se trata de un diseño RISC que ejecuta una instrucción cada 4 ciclos del oscilador.

En 1985, dicha división de microelectrónica de General Instruments se convirtió en una filial y el nuevo propietario canceló casi todos los desarrollos, que para esas fechas la mayoría estaban obsoletos. El PIC, sin embargo, se mejoró con EPROM para conseguir un controlador de canal programable. Hoy en día multitud de PICs vienen con varios periféricos incluidos (módulos de comunicación serie, UARTs, núcleos de control de motores, etc.) y con memoria de programa desde 512 a 32.000 palabras (una palabra corresponde a una instrucción en ensamblador, y puede ser 12, 14 o 16 bits, dependiendo de la familia específica de PICmicro).

El PIC usa un juego de instrucciones tipo RISC, cuyo número puede variar desde 35 para PICs de gama baja a 70 para los de gama alta. Las instrucciones se clasifican entre las que realizan operaciones entre el acumulador y una constante, entre el acumulador y una posición de memoria, instrucciones de condicionamiento y de salto/retorno, implementación de interrupciones y una para pasar a modo de bajo consumo llamada sleep.

Microchip proporciona un entorno de desarrollo freeware llamado MPLAB que incluye un simulador software y un ensamblador. Otras empresas desarrollan compiladores C y BASIC. Microchip también vende compiladores para los PICs de gama alta ("C18" para la serie F18 y "C30" para los dsPICs) y se puede descargar una edición para estudiantes del C18 que inhabilita algunas opciones después de un tiempo de evaluación.

Figura 2.12 Microcontrolador PIC.

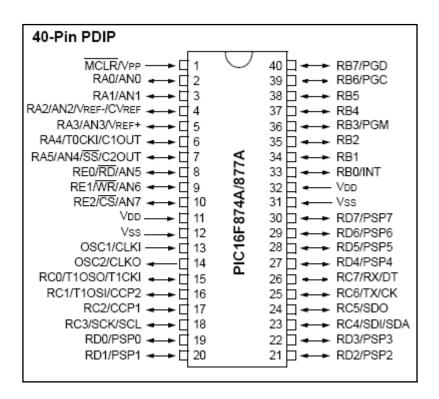

#### 2.3.1 Microcontrolador PIC16F877A

El microcontrolador PIC16F877A de Microchip pertenece a una gran familia de microcontroladores de 8 bits (bus de datos) que tienen las siguientes características generales que los distinguen de otras familias:

- -Arquitectura Harvard

- -Tecnología RISC

- -Tecnología CMOS

Estas características se conjugan para lograr un dispositivo altamente eficiente en el uso de la memoria de datos y programa y por lo tanto en la velocidad de ejecución.

La siguiente es una lista de las características del PIC16F877

- CPU RISC

- Sólo 35 instrucciones que aprender

- Todas las instrucciones se ejecutan en un ciclo de reloj, excepto los saltos que requieren dos

- Frecuencia de operación de 0 a 20 MHz (DC a 200 nseg de ciclo de instrucción).

- Hasta 8k x 14 bits de memoria Flash de programa.

- Hasta 368 bytes de memoria de datos (RAM).

- Hasta 256 bytes de memoria de datos EEPROM.

- Hasta 4 fuentes de interrupción.

- Stack de hardware de 8 niveles.

- Reset de encendido (POR).

- Timer de encendido (PWRT).

- Timer de arrangue del oscilador (OST)

- Sistema de vigilancia Watchdog timer.

- Protección programable de código.

- Modo SLEEP de bajo consumo de energía.

- Opciones de selección del oscilador

- Programación y depuración serie "In-Circuit" (ICSP) a través de dos patitas

- Lectura/escritura de la CPU a la memoria flash de programa

- Rango de voltaje de operación de 2.0 a 5.5 volts

- Alta disipación de corriente de la fuente: 25mA

- Empaquetado de 40 patitas (Fig. 2.13).

- Tecnología de la memoria incluida (EPROM, ROM, Flash)

- Voltajes de operación (desde 2.5 v. Hasta 6v)

- Frecuencia de operación (Hasta 20 MHz)

- Rangos de temperatura: Comercial, Industrial y Extendido

- Bajo consumo de potencia:

- \* Menos de 0.6mA a 3V, 4 MHz

- \* 20 µA a 3V, 32 KHz

- \* Menos de 1µA corriente de standby.

Figura 2.13 Diagrama de pines PIC 16F877A.

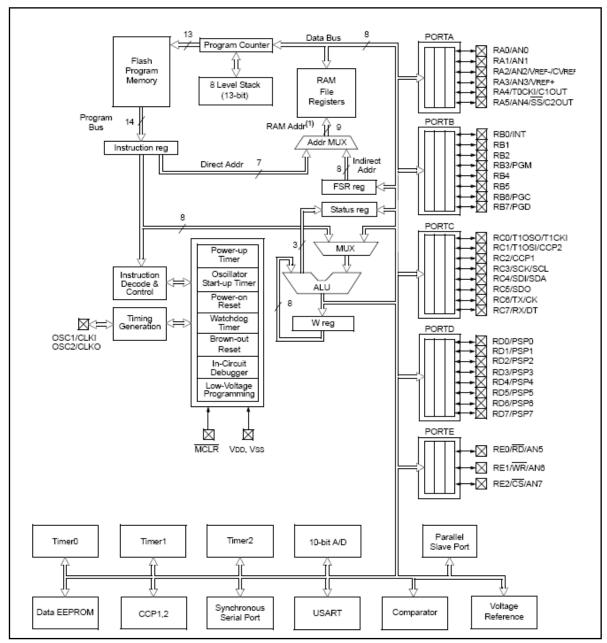

### 2.3.1.1Diagrama de Bloques del PIC16F877

En la siguiente figura se muestra a manera de bloques la organización interna del PIC16F877, Se muestra también junto a este diagrama su diagrama de pines para tener una visión conjunta del interior y exterior del Chip.

Figura 2.14 Diagrama a bloques PIC16F877A.

#### 2.3.1.2 Descripción de la CPU.

La CPU es la responsable de la interpretación y ejecución de la información (instrucciones) guardada en la memoria de programa.

Muchas de estas instrucciones operan sobre la memoria de datos.

Para operar sobre la memoria de datos además, si se van a realizar operaciones lógicas o aritméticas, requieren usar la Unidad de Lógica y Aritmética (ALU). La ALU controla los bits de estado (Registro STATUS), los bits de este registro se alteran dependiendo del resultado de algunas instrucciones.

#### 2.3.1.3Registros de la CPU.

Registro PC.- Registro de 13 bits que siempre apunta a la siguiente instrucción a ejecutarse. En la siguiente sección se dan mayores detalles en el manejo de este registro.

Registro de Instrucción.- Registro de 14 bits. Todas las instrucciones se colocan en el para ser decodificadas por la CPU antes de ejecutarlas.

Registro W.- Registro de 8 bits que guarda resultados temporales de las operaciones realizadas por la ALU

Registro STATUS.- Registro de 8 bits, cada uno de sus bits (denominados Banderas) es un indicador de estado de la CPU o del resultado de la última operación como se indica en la siguiente figura:

| . R/W-0          | R/W-0           | R/W-0          | R-1            | R-1       | R/W-x | R/W-x | R/W-x |

|------------------|-----------------|----------------|----------------|-----------|-------|-------|-------|

| IRP              | RP1             | RP0            | TO'            | PD'       | Ζ     | DC    | С     |

| Bit 7            | 6               | 5              | 4              | 3         | 2     | 1     | Bit 0 |

| R= Bit legible \ | W= Bit Escribib | le U= No imple | mentado (se le | e como 0) |       |       |       |

| n_ \/olor doon   | uóa dal Basat a | la anaondida   |                |           |       |       |       |

<sup>-</sup>n= Valor después del Reset de encendido

- Z.- Este bit se pone (=1) para indicar que el resultado de la última operación fue cero, de lo contrario se limpia (=0)

- C.- Bit de "acarreo/préstamo" de la última operación aritmética (en el caso de resta, se guarda el préstamo invertido

- CD.- "Acarreo/Préstamo" proveniente del cuarto bit menos significativo.

Funciona igual que el bit C, pero para operaciones de 4 bits.

Figura 2.15 Registro status.

En la siguiente tabla se resumen las 35 instrucciones (Fig. 2.16) que reconoce la CPU de los PIC de medio rango, tiempo de ejecución, código de máquina y afectación de banderas:

| Mnemónico  | Descripción                    | Ciclos    | Código de Máquina     | Banderas<br>afectadas |

|------------|--------------------------------|-----------|-----------------------|-----------------------|

| C          | peraciones con el archivo de   | eregistr  | os orientadas a bytes |                       |

| ADDWF f,d  | Suma f + W                     | 1         | 00 0111 dfff ffff     | C,DC,Z                |

| ANDWF f,d  | W AND f                        | 1         | 00 0101 dfff ffff     | Z                     |

| CLRF f     | Limpia f                       | 1         | 00 0001 1fff ffff     | Z                     |

| CLRW       | Limpia W                       | 1         | 00 0001 0xxx xxxx     | Z                     |

| COMF f.d   | Complementa los bits de f      | 1         | 00 1001 dfff ffff     | Z                     |

| DECF f,d   | Decrementa f en 1              | 1         | 00 0011 dfff ffff     | Z                     |

| DECFSZ f,d | Decrementa f, escapa si 0      | 1(2)      | 00 1011 dfff ffff     |                       |

| INCF f,d   | Incrementa f en 1              | 1         | 00 1010 dfff ffff     | Z                     |

| INCFSZ f,d | Incrementa f, escapa si 0      | 1(2)      | 00 1111 dfff ffff     |                       |

| IORWF f,d  | W OR f                         | 1         | 00 0100 dfff ffff     | Z                     |

| MOVF f,d   | Copia el contenido de f        | 1         | 00 1000 dfff ffff     | Z                     |

| MOVWF f    | Copia contenido de W en f      | 1         | 00 0000 1fff ffff     |                       |

| NOP        | No operación                   | 1         | 00 0000 0xx0 0000     |                       |

| RLF f,d    | Rota f a la izquierda          | 1         | 00 1101 dfff ffff     | С                     |

| RRF f,d    | Rota f a la derecha            | 1         | 00 1100 dfff ffff     | С                     |

| SUBWF f.d  | Resta f – W                    | 1         | 00 0010 dfff ffff     | C.DC.Z                |

|            | Intercambia nibbles de f       | 1         | 00 1110 dfff ffff     |                       |

| XORWF f,d  | W EXOR f                       | 1         | 00 0110 dfff ffff     | Z                     |

|            | Operaciones con el archivo d   | le regist | ros orientadas a bits | •                     |

| BCF f,b    | Limpia bit b en f              | 1         | 01 00bb bfff ffff     |                       |

| BSF f,b    | Pone bit b en f                | 1         | 01 01bb bfff ffff     |                       |

| BTFSC f,b  | Prueba bit b en f, escapa si 0 | 1(2)      | 01 10bb bfff ffff     |                       |

| BTFSS f,b  | Prueba bit b en f, escapa si 1 | 1(2)      | 01 11bb bfff ffff     |                       |

|            | Operaciones con lit            | erales y  |                       |                       |

| ADDLW k    | Suma literal k + W             | 1         | 11 111x kkkk kkkk     | C,DC,Z                |

| ANDLW k    | k AND W                        | 1         | 11 1001 kkkk kkkk     | Z                     |

| CALL k     | Llamado a subrutina            | 2         | 10 0kkk kkkk kkkk     |                       |

| CLRWDT     | Limpia timer del watchdog      | 1         | 00 0000 0110 0100     | TO',PD'               |

| GOTO k     | Salto a la dirección k         | 2         | 10 1kkk kkkk kkkk     |                       |

| IORLW k    | k OR W                         | 1         | 11 0000 kkkk kkkk     | Z                     |

| MOVLW k    | Copia literal a W              | 1         | 11 00xx kkkk kkkk     |                       |

| RETFIE     | Retorna de interrupción        | 2         | 00 0000 0000 1001     |                       |

| RETLW k    | Retorna con literal k en W     | 2         | 11 01xx kkkk kkkk     |                       |

| RETURN     | Retorna de subrutina           | 2         | 00 0000 0000 1000     |                       |

| SLEEP      | Activa Modo standby            | 1         | 00 0000 0110 0011     | TO'PD'                |

| SUBLW k    | Resta k - W                    | 1         | 11 110x kkkk kkkk     | C,CD,Z                |

| XORLW k    | k EXOR W                       | 1         | 11 1010 kkkk kkkk     | Z                     |

Figura 2.16 Tabla de instrucciones del PIC 16F877A

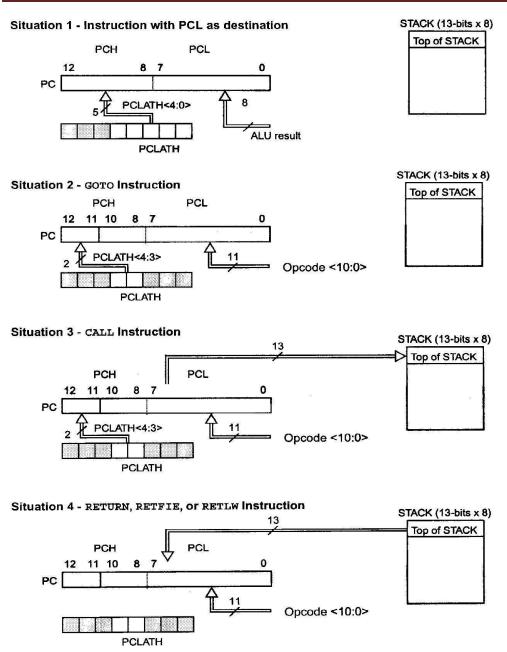

#### 2.3.1.4 Organización de la memoria del PIC

Los PIC tienen dos tipos de memoria: Memoria de Datos y Memoria de programa, cada bloque con su propio bus: Bus de datos y Bus de programa; por lo cual cada bloque puede ser accesado durante un mismo ciclo de oscilación.

La Memoria de datos a su vez se divide en:

- Memoria RAM de propósito general

- Archivo de Registros (Special Function Registres (SFR))

#### 2.6.1.- La Memoria de Programa

Los PIC de rango medio poseen un registro Contador del Programa (PC) de 13 bits, capaz de direccionar un espacio de 8K x 14, como todas las instrucciones son de 14 bits, esto significa un bloque de 8k instrucciones. El bloque total de 8K x 14 de memoria de programa está subdividido en 4 páginas de 2K x 14.

#### 2.3.1.5 La Memoria de Datos

La memoria de datos consta de dos áreas mezcladas y destinadas a funciones distintas:

- Registros de Propósito Especial (SFR)

- Registro de Propósito General (GPR)

Los SFR son localidades asociadas específicamente a los diferentes periféricos y funciones de configuración del PIC y tienen un nombre específico asociado con su función. Mientras que los GPR son memoria RAM de uso general.

#### 2.3.1.6 Bancos de memoria

Toda la memoria de datos está organizada en 4 *bancos* numerados 0, 1, 2 y 3. Para seleccionar un banco se debe hacer uso de los bits del registro STATUS<7:5> denominados IRP, RP1 y RP0 (Fig. 2.17).

Hay dos maneras de acceder a la memoria de datos:

Direccionamiento directo e indirecto. La selección de bancos se basa en la siguiente tabla

| Direccionamiento<br>Indirecto (IRP) | RP1:RP0 | Banco |

|-------------------------------------|---------|-------|

| 0                                   | 0 0     | 0     |

| U                                   | 0 1     | 1     |

| 1                                   | 10      | 2     |

| '                                   | 11      | 3     |

Figura 2.17 Bancos de memoria.

Cada banco consta de 128 bytes (de 00h a 7Fh). En las posiciones más bajas de cada banco se encuentran los SFR, y arriba de éstos se encuentran los GPR. Toda la memoria de datos está implementada en RAM estática.

Direccionamiento Directo. Para acceder una posición de memoria mediante direccionamiento directo, la CPU simplemente usa la dirección indicada en los 7 bits menos significativos del código de operación y la selección de banco de los bits RP1:RP0.

Direccionamiento indirecto. Este modo de direccionamiento permite acceder una localidad de memoria de datos usando una dirección de memoria *variable* a diferencia del direccionamiento directo, en que la dirección es fija. Esto puede ser útil para el manejo de tablas de datos.

#### 2.3.1.7 El Archivo de Registros

Aunque el archivo de registros en RAM puede variar de un PIC a otro, la familia del PIC16F87x coincide casi en su totalidad. En la siguiente figura se muestra a detalle el mapa de este archivo de registros y su organización en los cuatro bancos que ya se describieron.

| ,                              | File<br>Address | A                              | File<br>kddress | ,                              | File<br>Address |                                |

|--------------------------------|-----------------|--------------------------------|-----------------|--------------------------------|-----------------|--------------------------------|

| Indirect addr.(*)              | 00h             | Indirect addr.(*)              | 80h             | Indirect addr.(*)              | 100h            | Indirect addr.(*)              |

| TMR0                           | 01h             | OPTION REG                     | 81h             | TMR0                           | 101h            | OPTION_REG                     |

| PCL                            | 02h             | PCL                            | 82h             | PCL                            | 102h            | PCL                            |

| STATUS                         | 03h             | STATUS                         | 83h             | STATUS                         | 103h            | STATUS                         |

| FSR                            | 04h             | FSR                            | 84h             | FSR                            | 104h            | FSR                            |

| PORTA                          | 05h             | TRISA                          | 85h             | 2                              | 105h            |                                |

| PORTB                          | 06h             | TRISB                          | 86h             | PORTB                          | 106h            | TRISB                          |

| PORTC                          | 07h             | TRISC                          | 87h             | 7 1 7 2 7 1 1                  | 107h            | 5                              |

| PORTD <sup>(1)</sup>           | 08h             | TRISD <sup>(1)</sup>           | 88h             | 7 22 3                         | 108h            |                                |

| PORTE <sup>(1)</sup>           | 09h             | TRISE <sup>(1)</sup>           | 89h             | The state of the               | 109h            |                                |

| PCLATH                         | 0Ah             | PCLATH                         | 8Ah             | PCLATH                         | 10Ah            | PCLATH                         |

| INTCON                         | 0Bh             | INTCON                         | 8Bh             | INTCON                         | 10Bh            | INTCON                         |

| PIR1                           | 0Ch             | PIE1                           | 8Ch             | EEDATA                         | 10Ch            | EECON1                         |

| PIR2                           | 0Dh             | PIE2                           | 8Dh             | EEADR                          | 10Dh            | EECON2                         |

| TMR1L                          | 0Eh             | PCON                           | 8Eh             | EEDATH                         | 10Eh            | Reserved <sup>(2)</sup>        |

| TMR1H                          | 0Fh             | CONTRACTOR                     | 8Fh             | EEADRH                         | 10Fh            | Reserved <sup>(2)</sup>        |

| T1CON                          | 10h             | 534 -7 - 3 -9                  | 90h             |                                | 110h            |                                |

| TMR2                           | 11h             | SSPCON2                        | 91h             |                                | 111h            |                                |

| T2CON                          | 12h             | PR2                            | 92h             |                                | 112h            |                                |

| SSPBUF                         | 13h             | SSPADD                         | 93h             |                                | 113h            |                                |

| SSPCON                         | 14h             | SSPSTAT                        | 94h             |                                | 114h            | 1                              |

| CCPR1L                         | 15h             |                                | 95h             |                                | 115h            |                                |

| CCPR1H                         | 16h             |                                | 96h             |                                | 116h            |                                |

| CCP1CON                        | 17h             | J-1 5 F 13                     | 97h             | General                        | 117h            | General                        |

| RCSTA                          | 18h             | TXSTA                          | 98h             | Purpose<br>Register            | 118h            | Purpose<br>Register            |

| TXREG                          | 19h             | SPBRG                          | 99h             | 16 Bytes                       | 119h            | 16 Bytes                       |

| RCREG                          | 1Ah             | C. D. I.O                      | 9Ah             | 10 27.00                       | 11Ah            | , , , , ,                      |

| CCPR2L                         | 1Bh             | V 7 F 4                        | 9Bh             |                                | 11Bh            |                                |

| CCPR2H                         | 1Ch             |                                | 9Ch             |                                | 11Ch            |                                |

| CCP2CON                        | 1Dh             |                                | 9Dh             |                                | 11Dh            | ,                              |

| ADRESH                         | 1Eh             | ADRESL                         | 9Eh             |                                | 11Eh            |                                |

| ADCON0                         | 1Fh             | ADCON1                         | 9Fh             | 1                              | 11Fh            | 1                              |

| ADCONU                         | 20h             | ADCONT                         |                 |                                | 120h            |                                |

| General<br>Purpose<br>Register | 2011            | General<br>Purpose<br>Register | A0h             | General<br>Purpose<br>Register |                 | General<br>Purpose<br>Register |

|                                |                 | 80 Bytes                       |                 | 80 Bytes                       | 16Fh            | 80 Bytes                       |

| 96 Bytes                       |                 | accesses<br>70h-7Fh            | EFh<br>F0h      | accesses<br>70h-7Fh            | 170h            | accesses<br>70h - 7Fh          |

| Bank 0                         | J 7Fh           | Bank 1                         | FFh             | Bank 2                         | 2 17711         | Bank 3                         |

Unimplemented data memory locations, read as '0'.

Not a physical register.

Figura 2.18 Mapa de archivo de registros.

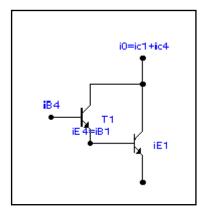

#### 2.4 ARREGLO DARLINGTON DE TRANSISTORES

El amplificador Darlington (frecuentemente llamado amplificador compuesto) es una conexión muy popular de dos transistores de unión bipolar para funcionar como un solo transistor "superbeta" (Fig.2.21), la conexión Darlington se muestra en la figura 8.1.La principal característica de la conexión Darlington es que el transistor compuesto actúa como una sola unidad con una ganancia de corriente que es el producto de las ganancias de corriente de dos transistores por separado. Si la conexión se hace utilizando dos transistores individuales con ganancias de corriente de  $\beta1$  y  $\beta2$  la conexión Darlington proporciona una ganancia de corriente de:

$$\beta_D = \beta_1 \beta_2$$

Una conexión de transistor Darlington proporciona un transistor con una ganancia de corriente de varios miles.

Figura 2.21 Amplificador Darlington Básico.

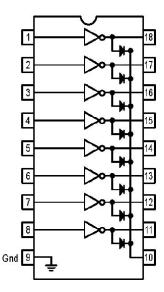

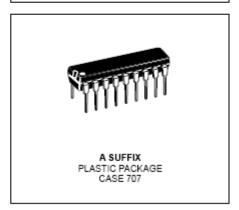

#### 2.4.1 Arreglo Darlington de transistores ULN2803A

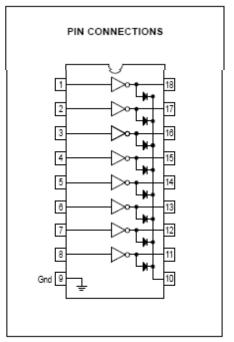

Los ocho transistores NPN conectados en arreglo Darlington (Fig. 2.22) son ideales para una interfaz entre la lógica de bajo nivel de circuitos digitales (como TTL, CMOS o OGP / NMOS) y el actual superior / requisitos de voltaje de las lámparas, relés, impresoras, martillos u otras cargas similares para una amplia gama de equipo industrial y aplicaciones de consumo. Todos los dispositivos con la característica de colector abierto y libre de productos de sujeción de rueda de diodos de supresión transitoria (Fig. 2.23, 2.25).

El ULN2803 está diseñado para ser compatible con el estándar de las familias TTL, mientras que el ULN2804 está optimizado para 6 a 15 voltios de alto nivel o CMOS OGP.

Figura 2.22 Diagrama de conexiones.

| Rating                              | Symb<br>ol | Value           | Unit |

|-------------------------------------|------------|-----------------|------|

| Output Voltage                      | VO         | 50              | V    |

| Input Voltage (Except ULN2801)      | VI         | 30              | V    |

| Collector Current –<br>Continuous   | IC         | 500             | mA   |

| Base Current – Continuous           | ΙB         | 25              | mΑ   |

| Operating Ambient Temperature Range | TA         | 0 to +70        | °C   |

| Storage Temperature Range           | Tstg       | – 55 to<br>+150 | °C   |

| Junction Temperature                | TJ         | 125             | °C   |

Figura 2.23 Características ULN2803.

Figura 2.24 Diagrama esquemático.

OUTLINE DIMENSIONS

# A SUFFIX PLASTIC PACKAGE CASE 707-02 ISSUE C NOTES: 1. POSITIONAL TOLERANCE OF LEADS (D). SHALL BE WITHIN 0.25 (D.10) AT MAXIM.M MATERIAL CONDITION. IN RELIATION TO SEATING PLANE AND EACH OTHER. 2. DIMENSION IS DOES NOT INCLIDE MOLD RASH. MILLIMETERS INCHES I

Figura 2.25 Dimensiones y encapsulado ULN2803

### 2.5 MOTORES A PASOS

El motor de paso a paso es un dispositivo electromecánico que convierte una serie de impulsos eléctricos en desplazamientos angulares discretos, lo que significa es que es capaz de avanzar una serie de grados (paso) dependiendo de sus entradas de control. El motor paso a paso se comporta de la misma manera que un convertidor digital-analógico y puede ser gobernado por impulsos procedentes de sistemas lógicos.

Este motor presenta las ventajas de tener alta precisión y repetitividad en cuanto al posicionamiento. Entre sus principales aplicaciones destacan como motor de frecuencia variable, motor de corriente continua sin escobillas, servomotores y motores controlados digitalmente.

La variación de la dirección del campo magnético creado en el estator producirá movimiento de seguimiento por parte del rotor de imán permanente, el cual intentará alinearse con campo magnético inducido por las bobinas que excitan los electroimanes.

Figura 2.26 Motores a pasos.

### 2.6 PANTALLA LCD

Una pantalla de cristal líquido o LCD (acrónimo del inglés Liquid crystal display) es una pantalla delgada y plana formada por un número de píxeles en color o monocromos colocados delante de una fuente de luz o reflectora. A menudo se utiliza en dispositivos electrónicos de pilas, ya que utiliza cantidades muy pequeñas de energía eléctrica.

Cada píxel de un LCD típicamente consiste de una capa de moléculas alineadas entre dos electrodos transparentes, y dos filtros de polarización, los ejes de transmisión de cada uno están (en la mayoría de los casos) perpendiculares entre sí. Sin cristal líquido entre el filtro polarizante, la luz que pasa por el primer filtro sería bloqueada por el segundo (cruzando) polarizador (Fig. 2.27).

Figura 2.27 Pantalla LCD.

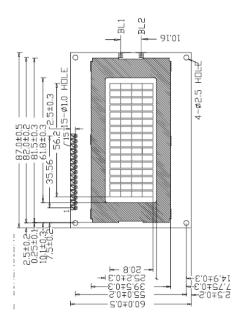

### 2.6.1 Pantalla LCD LM4433

El modulo de la pantalla consiste en un display de cristal líquido, un controlador (driver CMOS), circuito impreso, marco o base de metal e iluminación posterior a base de leds (diodo emisor de luz) (Fig. 2.28 y 2.29).

Figura 2.28 Dimensiones del display.

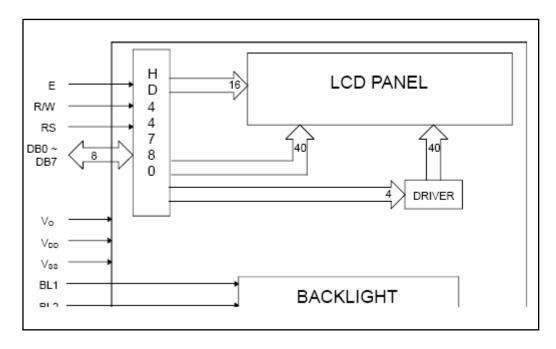

Figura 2.29 Esquema de conexiones del display.

| Pin No. | Symbol   | I/O | Function                                  |

|---------|----------|-----|-------------------------------------------|

| 1       | Vss, BL2 | -   | Ground (0V), VLED-                        |

| 2       | VDD      | -   | Logic Supply Voltage (+5V)                |

| 3       | Vo       | -   | LC Drive voltage for contrast adjustment  |

| 4       | RS       | I   | Register Select 0: Instruction Register   |

|         |          |     | 1: Data Register                          |

| 5       | RW       | I   | Read / Write 0: Data Write (Module ← MPU) |

|         |          |     | 1: Data Read (Module→ MPU)                |

| 6       | E        | I   | Enable Signal Active High (H→L)           |

| 7       | DB0      | 1/0 | Bi-directional data bus line 0            |

| 8       | DB1      | 1/0 | Bi-directional data bus line 1            |

| 9       | DB2      | I/O | Bi-directional data bus line 2            |

| 10      | DB3      | 1/0 | Bi-directional data bus line 3            |

| 11      | DB4      | I/O | Bi-directional data bus line 4            |

| 12      | DB5      | I/O | Bi-directional data bus line 5            |

| 13      | DB6      | I/O | Bi-directional data bus line 6            |

| 14      | DB7      | I/O | Bi-directional data bus line 7            |

| 15      | BL1      | -   | Supply voltage for backlight (+5V), VLED+ |

| BL1     | VLED+    | -   | Anode (+); LED backlight input voltage    |

| BL2     | VLED-    | -   | Cathode (-); LED backlight input voltage  |

Figura 2.30 Descripción de la interfaz.

# CAPÍTULO III. PROBLEMÁTICA

### 3.1 DESCRIPCIÓN DEL PROBLEMA

Como hemos mencionado anteriormente, este proyecto pretende ofrecer un sistema que permita desarrollar las labores relacionadas con la calificación de exámenes por medios computacionales. Esto es, la lectura del examen, comparación de resultados, cálculo de calificación con base en el número de aciertos del examen y la presentación de los mismos por conducto de un display en nuestro dispositivo y posteriormente a través de una interfaz hombre máquina. También se mencionó que las funciones del presente proyecto son tan ambiciosas que no podrán ser cubiertas por un sólo trabajo de tesis, dejando para un segundo trabajo la parte más compleja del procesamiento de datos, y que llamaremos "Bloque Complejo". Este bloque de software permitirá al maestro cumplir con tareas complicadas que en hipótesis tenemos identificadas y que parecen viables para incorporarse a esta parte del sistema y son las siguientes:

- Permitir al maestro introducir nuevos reactivos para acrecentar la base de datos. Estos reactivos estarán disponibles para la posteridad.

- De este conglomerado de reactivos podrá tomarse una muestra aleatoria para conformar un examen de un número de preguntas determinado por el mismo maestro.

- Permitir al maestro el tipo de pregunta (reactivo) que desee incluir en su diseño de examen, pudiendo ser de preguntas de opción múltiple o problemas.

- El sistema deberá incluir algoritmos de cálculo a disposición del maestro para permitirle determinar los resultados correctos de sus reactivos, y almacenarlos como datos válidos en cada pregunta.

- El sistema tendrá entonces los valores de referencia que serán usados para decidir si los resultados leídos del exterior (procedentes de la hoja de examen) son correctos.

- Permitir al maestro calificar y visualizar el resultado de un grupo de exámenes determinado.

- Permitir la impresión de los resultados.

- Permitir configurar el examen adecuadamente en casos en que el maestro decida calificar el procedimiento además de los resultados finales de cada problema.

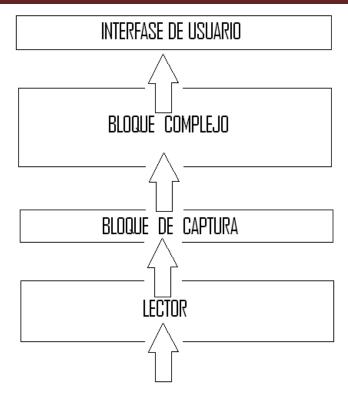

El siguiente esquema ilustra los bloques funcionales de que consta nuestra propuesta

En este esquema se ilustran los bloques que constituyen al sistema calificador basado en optosensores. Nótese que el primer bloque funcional del sistema es el lector, que se encarga de producir las señales binarias a partir de las hojas de examen e introducirlas al microcontrolador. Este bloque está elaborado con tecnología electrónica.

Figura 3.1 Diagrama a bloques del sistema

Después se encuentra el bloque de captura que se encarga de tomar los datos procedentes del lector y apilarlos en un espacio de memoria dentro del microcontrolador predefinido. Este bloque, está elaborado exclusivamente de software a bajo nivel.

Los dos bloques superiores del esquema se han pensado dejar pendientes debido a que se basan en las otras para su construcción y prueba, pero esto no significa que el trabajo de la primera etapa del proyecto sea inútil, por el contrario: esta etapa por sí misma, aunque simple, será capaz de llevar a cabo lo más importante de las funciones del proyecto, esto es, calificar y entregar calificaciones.

Para esto se necesita, en principio, una forma de obtener datos binarios a partir de la simbología escrita por los alumnos en el formato establecido. En otras palabras, se requiere que la información plasmada por los alumnos en su hoja de

respuesta, sea transformada a una forma que la computadora pueda reconocer y manejar. Esta importante función la realizará un módulo que llamaremos lector. Además, es necesario programar el microcontrolador para que permita tomar la información del lector y colocarla en un espacio de su memoria interna para realizar con ella las funciones más complejas de cálculos y decisiones requeridas para responder a las diversas solicitudes del maestro, como el cálculo de calificación, impresión de resultados, etc.

### CAPÍTULO IV. ESTADO DEL ARTE

# 4.1 SISTEMAS DE LECTURA ÓPTICA PARA EXÁMENES EN PAPEL IMPRESO.

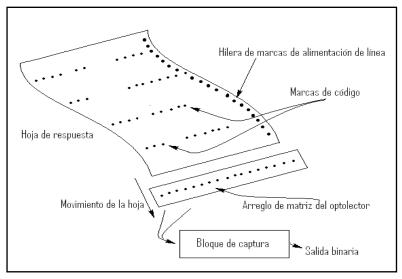

Actualmente existe una diversidad de lectores ópticos usados para aplicaciones semejantes a la de este problema. La más común es el empleo de arreglos matriciales de fotodiodos o fototransistores lineales para capturar variaciones de intensidad luminosa provenientes del papel. Estos dispositivos son suficientemente sensibles para producir un pulso eléctrico en el instante en que aparece un punto negro en el papel frente de él, además, cada sensor es de un tamaño tan pequeño que pueden manejarse puntos negros cuyo diámetro es del orden del milímetro.

Al deslizar el papel frente a los arreglos sensoriales, estos captan las variaciones de luz de cada punto y lo convierten en pulsos eléctricos independientes. Esta matriz entonces, produce una matriz de pulsos factibles de ser leídos por la computadora a manera de palabras de datos binarios.

Figura 4.1 Ilustración de los formatos de hojas en sistemas comerciales

Los sistemas comerciales de lectura de puntos están construidos con partes fabricadas ex profeso para estas funciones, así, las matrices de optolectores y circuitos impresos asociados son muy pequeños, así como los circuitos electrónicos ocupados para las diferentes funciones de amplificación, adaptación de señales y acoplamiento a la computadora están elaborados mediante pastillas electrónicas integradas elaboradas desde fábrica a gran escala. Asimismo, el software relacionado con los manejos computacionales de los datos capturados es muy complejo, caracterizándose por ser funcionales pero dando sobre todo un énfasis en la presentación.

Figura 4.2 Sistemas comerciales.

Además, estos sistemas disponen de un mecanismo de alimentación de hojas complicado, que permite la colocación de paquetes voluminosos de exámenes en su charola de entrada y esperar que el sistema tome una por una para terminar cómodamente con todo el conjunto de exámenes. Adicionalmente, tienen algunas funciones misceláneas como contador de hojas y tablero de mensajes para avisar al usuario el atascamiento de papel, fin de tarea, entre otras.

Todo esto con un costo que ronda los \$2000 USD.

Figura 4.3 Ilustración

Otras opciones en el mercado son las que se basan en nuevas tecnologías de software capaces de reconocer imágenes y caracteres predefinidos.

Figura 4.4 Otros ejemplos.

Este software permite que a través de un scanner se pueda reconocer letras manuscritas o imágenes y traducirlas a sistema ASCII para que la computadora sea capaz de leerlas y de realizar las operaciones necesarias para la evaluación de formularios y exámenes.

Algunas de estas tecnologías son ICR (Reconocimiento de caracteres inteligente), OCR (Reconocimiento de caracteres ópticos) y OMR (Lectura de marcas ópticas). Figura 4.5.

Figura 4.5 Tecnología ICR, OCR y OMR.

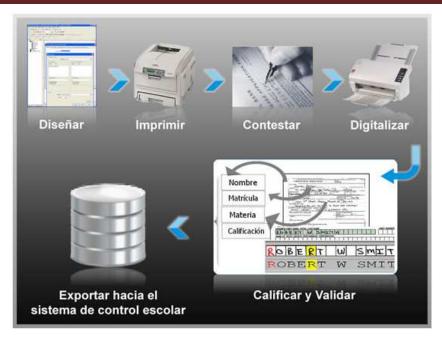

Remark Office OMR es uno de los sistemas en el mercado que usa tecnología OMR y funciona de la siguiente manera.

Remark Office OMR puede leer de sus fichas las áreas con marcas, así como información de códigos de barras. Los campos diligenciados a mano con máquina de escribir no pueden ser leídos por el software, pero pueden ser capturados como campos de imagen para que posteriormente un operador digite la información allí escrita o solamente para su visualización. El manejo de excepciones facilita la localización, corrección o verificación de cualquier ficha marcada erróneamente.

## Exportación de datos

Una vez que sus formas se han escaneado y procesado, el software puede guardar los datos en cerca de 30 formatos distintos, que pueden ser utilizados virtualmente en cualquier paquete de análisis como SPSS, dBase, Access, Excel o Lotus 1-2-3. Remark Office OMR puede incluso guardar sus datos en formato HTML para la publicación en Internet o una Intranet. También puede guardar sus

datos en el formato de Remark Office OMR y tomar ventaja de las herramientas analíticas propias del software.

ICR, OCR y OMR son todos métodos orientados a disminuir la cantidad de entradas de datos manual en ambientes de procesamiento de formularios. ICR y OCR son dispositivos de reconocimiento usados con imágenes. OMR es una tecnología de captura de datos que no requiere un dispositivo de reconocimiento, es utilizada cuando se requiere un alto grado de precisión.

### ICR – Reconocimiento de Caracteres Inteligente

La tecnología ICR proporciona a los sistemas de reproducción por escáner y sistemas de imágenes la habilidad de convertir caracteres en letra manuscrita (no cursiva) en caracteres capaces de ser interpretados o reconocidos por una computadora. Así, las imágenes de caracteres en letra manuscrita son extraídas de un mapa de bits de la imagen reproducida por el escáner. Existen diversos dispositivos de reconocimiento ICR en el mercado.

# OCR - Reconocimiento de Caracteres Ópticos

La tecnología OCR proporciona a los sistemas de reproducción por escáner y sistemas de imágenes la habilidad de convertir imágenes de caracteres en letra de máquina, en caracteres capaces de ser interpretados o reconocidos por una computadora. Así, las imágenes de caracteres en letra de máquina son extraídas de un mapa de bits de la imagen reproducida por el escáner.

# OMR – Lectura de Marcas Ópticas

La tecnología OMR detecta la ausencia o presencia de una marca, pero no la forma de la marca. El software interpreta la imagen del escáner y la traduce en la imagen deseada ASCII. Los formularios son reproducidos por escáner a través de un escáner OMR. Los formularios contienen pequeños círculos, llamados "burbujas", que son completados por la persona encargada de llenar el formulario.

La tecnología OMR no es capaz de reconocer caracteres en letra manuscrita o a máquina; las imágenes de los formularios tampoco son reproducidas por el escáner.

Un escáner de reproducción de imágenes es capaz de procesar entre 1.200 y 7.500 formularios por hora. Sin embargo, no es la velocidad de reproducción del escáner la que determina la productividad de una aplicación. Otros factores influyen en esta variable, tales como la cantidad de caracteres por página, el número de distintos tipos de documentos y el grado de legibilidad de la letra manuscrita. Un escáner de reproducción de imágenes es significativamente más costoso que un escáner OMR. A medida que el volumen de reproducción por escáner aumenta, se requiere una red de terminales y servidores para procesar dicha actividad. Una aplicación esta rara vez limitada por la velocidad de reproducción del escáner, puede estar en cambio, limitada por el poder de procesamiento de la red.

Un escáner OMR es capaz de mantener un nivel de procesamiento de 2.000 a 10.000 formularios por hora. Esta actividad puede ser controlada y procesada por una sola terminal, que a su vez es capaz de manipular cualquier volumen que el escáner genere. Incrementar la capacidad de procesamiento simplemente requiere mejorar el tipo de escáner. Los software ICR y OCR no pueden ser utilizados con un escáner OMR.

### CAPÍTULO V. SOLUCIÓN PROPUESTA.

### 5.1 IDENTIFICACIÓN DE NECESIDADES Y CARACTERÍSTICAS.

Por lo anteriormente expuesto, los sistemas comerciales, permiten un uso cómodo, presentable y eficiente pero conllevan así mismo una dependencia económica y tecnológica indiscutible porque se acompañan de un diseño respaldado por una marca comercial establecida, aspectos que difícilmente se podrá alcanzar con métodos improvisados como los de esta propuesta (Fig.5.1). Nosotros pensamos que, usando tecnología propia, es posible alcanzar los niveles de eficiencia suficientes como para satisfacer las necesidades más importantes de las actividades docentes promedio. Esto es, empleando dispositivos que puedan conseguirse en forma fácil en cualquier tienda especializada en electrónica y con un costo muy reducido.

Figura 5.1 Funcionamiento general del sistema óptico pretendido.

El diseño propuesto respeta básicamente el mismo esquema de la figura 5.1, pero se decidió darle movilidad al lector en vez de a la hoja utilizando el sistema de un escáner común reduciendo las funciones hasta el mínimo necesario para cumplir con las funciones básicas (Fig. 5.2): Capturar, evaluar y calificar los resultados que se encuentran en cada hoja de examen alimentada.

Figura 5.2 Modelo propuesto.

Análogamente, el programa diseñado para la etapa inicial, según se mencionó anteriormente, cumplirá con las funciones indispensables para el manejo de los datos, desde la captura, hasta la entrega de resultados al usuario a través de una interface sencilla.

Para esto y tomando en cuenta la baja sensibilidad presentada por los optosensores corrientes, se plantea adicionar una fuente de luz colocada por debajo de la hoja de examen, con el fin de asegurar la suficiente reacción de los lectores ópticos.

### 5.2 DISEÑO DEL SISTEMA ÓPTICO.

Para el sistema óptico, proponemos el empleo de fototransistores independientes modelo PT331C, arreglados en forma de matriz para constituir un bloque lector, de tal forma que no represente una dificultad su consecución. Las dimensiones de los dispositivos ópticos más comunes (5mm) se adaptan casi exactamente a las

necesidades del formato diseñado para la hoja de respuestas (Fig. 5.3), de tal manera que nos es posible alinear y hacer coincidir los fototransistores en cada hilera de nuestro modelo (Fig. 5.4)

Figura 5.3 Sistema óptico

Como el alumno marcará con lápiz algunos espacios en nuestra hoja de respuestas, entonces la parte sombreada limitará el reflejo de luz hacia el sensor, propiciando una drástica disminución de señal eléctrica, estados en que se logrará un "cero" lógico. Este efecto lo lograremos a través de la reflexión de la luz incidente en nuestra propia hoja, de tal forma que será necesario colocar una fuente de luz intensa en el ángulo adecuado entre la hoja de respuestas y el sistema óptico de manera que la luz reflejada en los sensores sea suficiente para mantener el nivel de luz correspondiente a un "uno" lógico.

Figura 5.4 posición de los sensores ópticos.

### 5.3 MOVILIDAD DEL LECTOR.

Para darle movimiento a nuestro sistema óptico hemos recurrido al uso de un motor a pasos

que será controlado por el microcontrolador y nos dará la movilidad exacta y necesaria para que el sistema pueda detectar atinadamente cada una de las guías que nos presenta la hoja de respuestas, así como las opciones seleccionadas por el alumno.

Esta etapa estará ligada estrechamente con el sistema óptico, que será el que de la señal para que se detenga el motor en cada renglón. La línea de control obtenida en la etapa óptica será enviada directamente al microcontrolador y este nos dará cuatro señales que ingresaran al driver ULN2803, Fig. 5.5 (que es un arreglo Darlington de transistores) capaz de darle la movilidad necesaria a nuestro motor.

Figura 5.5 Diagrama esquemático ULN2803A

### 5.4 ILUMINACIÓN.

El sistema de iluminación mencionado será propiciado mediante una lámpara tipo "Slim-Line" de 23 cm de longitud, con alimentación del balastro de 12 volts c.d. a 1 Amp. El cual eleva este voltaje hasta cerca de 1000 volts.

### 5.5 MULTIPLEXIÓN.

La siguiente etapa será la de multiplexión de los pulsos obtenidos por el sistema óptico descrito.